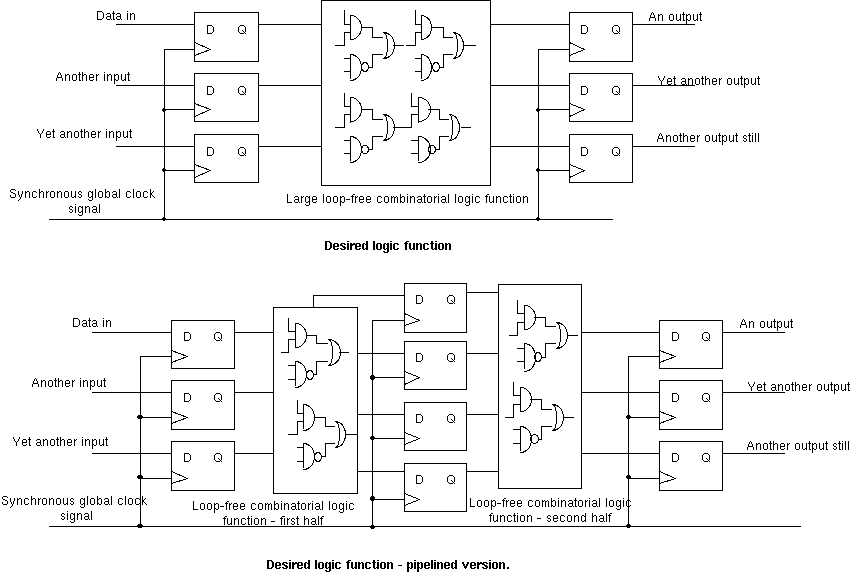

A previously proposed design for eliminating the performance penalty of... | Download Scientific Diagram

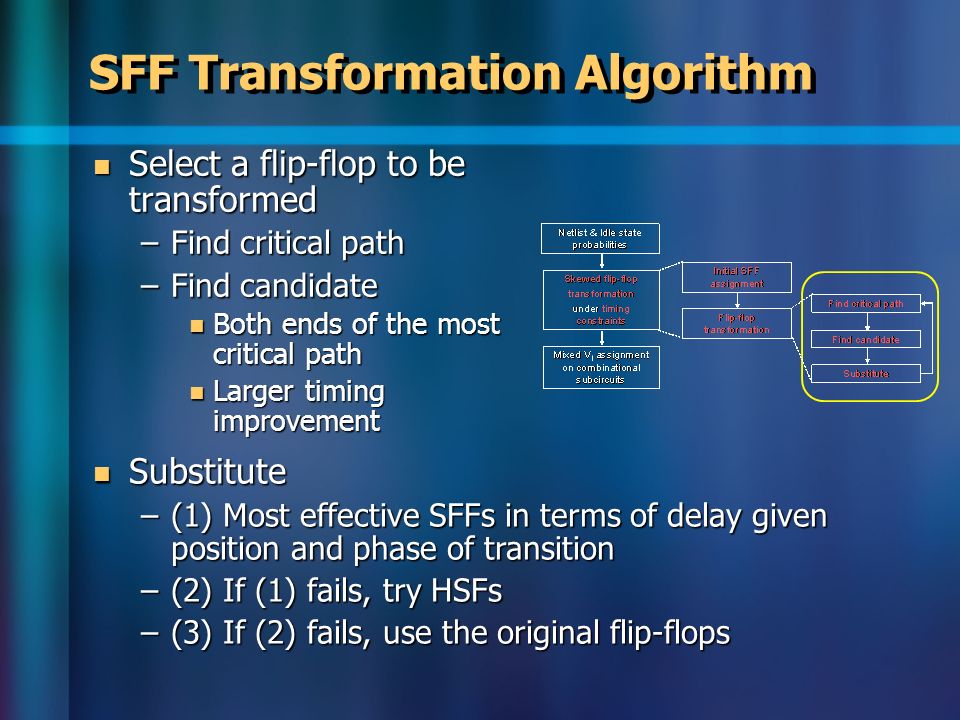

Skewed Flip-Flop Transformation for Minimizing Leakage in Sequential Circuits Jun Seomun, Jaehyun Kim, Youngsoo Shin Dept. of Electrical Engineering, KAIST, - ppt download

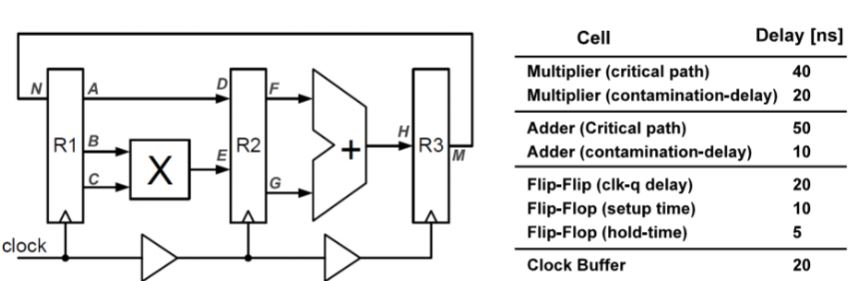

Figure 2 | A Modified Implementation of Tristate Inverter Based Static Master-Slave Flip-Flop with Improved Power-Delay-Area Product

![PDF] VLSI implementation of CRC-32 for 10 Gigabit Ethernet | Semantic Scholar PDF] VLSI implementation of CRC-32 for 10 Gigabit Ethernet | Semantic Scholar](https://d3i71xaburhd42.cloudfront.net/c4d5d70c337b1ffeb1e615d04e62dc4293d34b9e/2-Figure2-1.png)