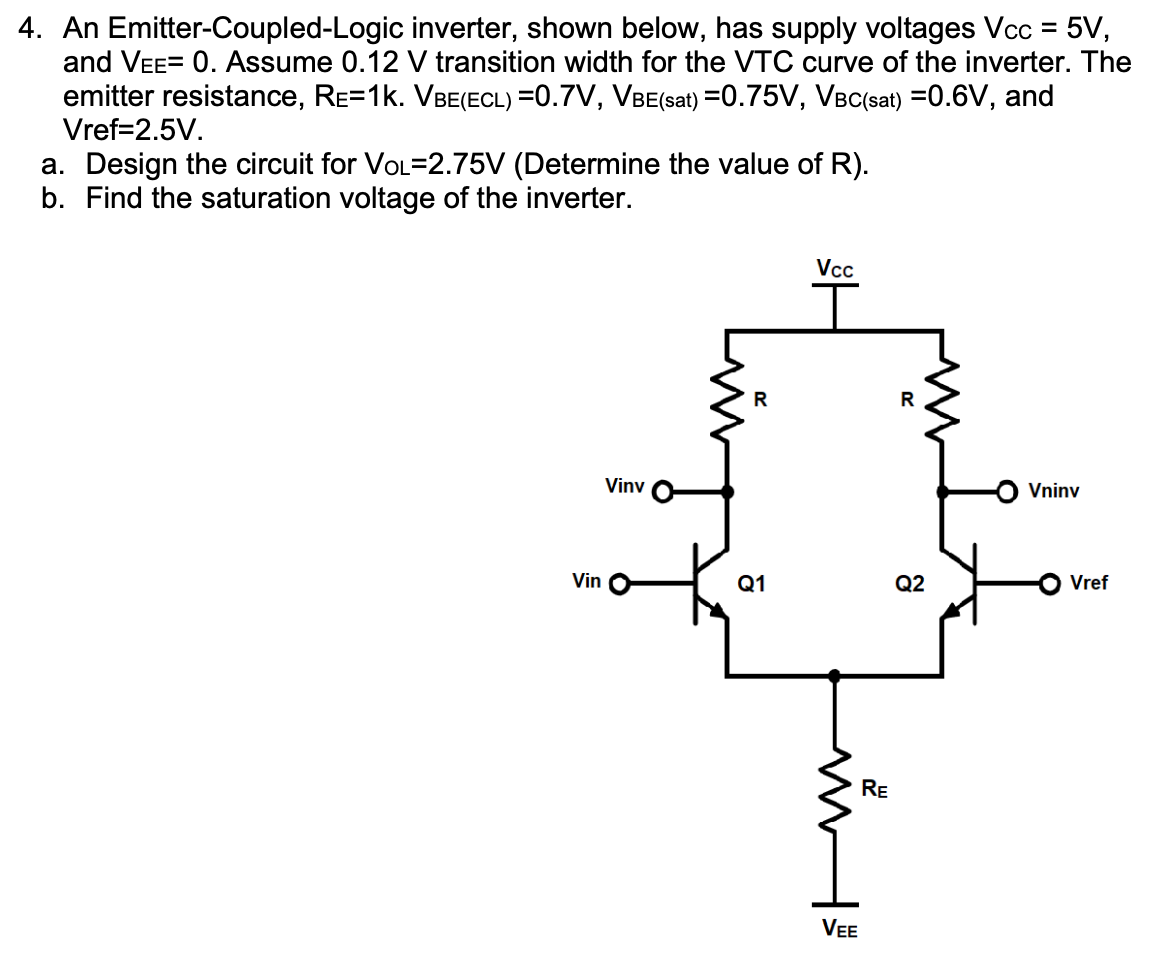

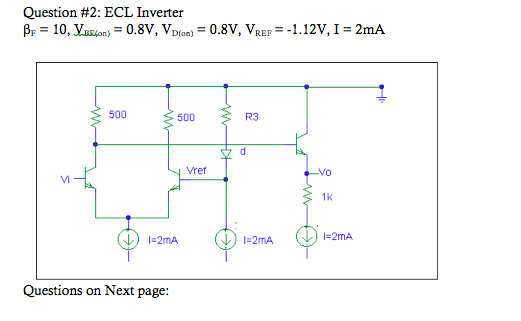

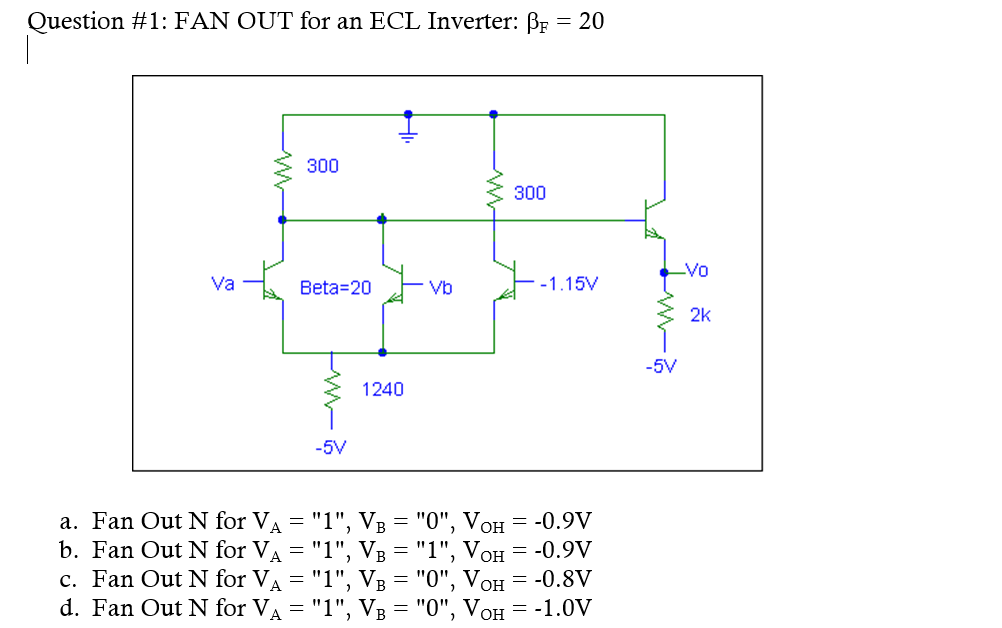

ecl.doc - Homework #6: ECL Note on drawing from PSPICE: if a node is not indicated, the lines do not touch. Question #1: FAN OUT for an ECL Inverter: F | Course Hero

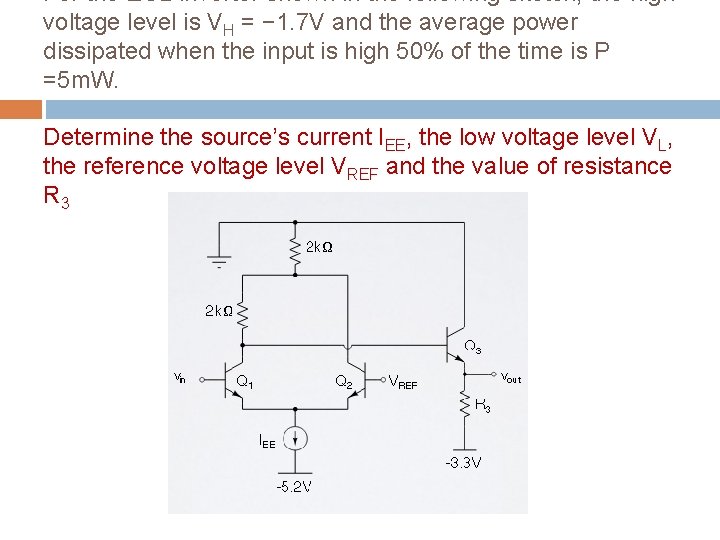

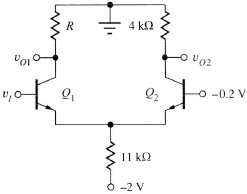

Write report about Study and analyze noise margin of the ECL inverter. Write report about Study... - HomeworkLib