![4.8 VHDL Operators - Introduction to Digital Systems: Modeling, Synthesis, and Simulation Using VHDL [Book] 4.8 VHDL Operators - Introduction to Digital Systems: Modeling, Synthesis, and Simulation Using VHDL [Book]](https://www.oreilly.com/library/view/introduction-to-digital/9780470900550/images/ch004-f018.jpg)

4.8 VHDL Operators - Introduction to Digital Systems: Modeling, Synthesis, and Simulation Using VHDL [Book]

VHDL & FPGA Design Expert - MATLAB Sole Distributor | TechSource Systems & Ascendas Systems Group | MATLAB Sole Distributor | TechSource Systems & Ascendas Systems Group

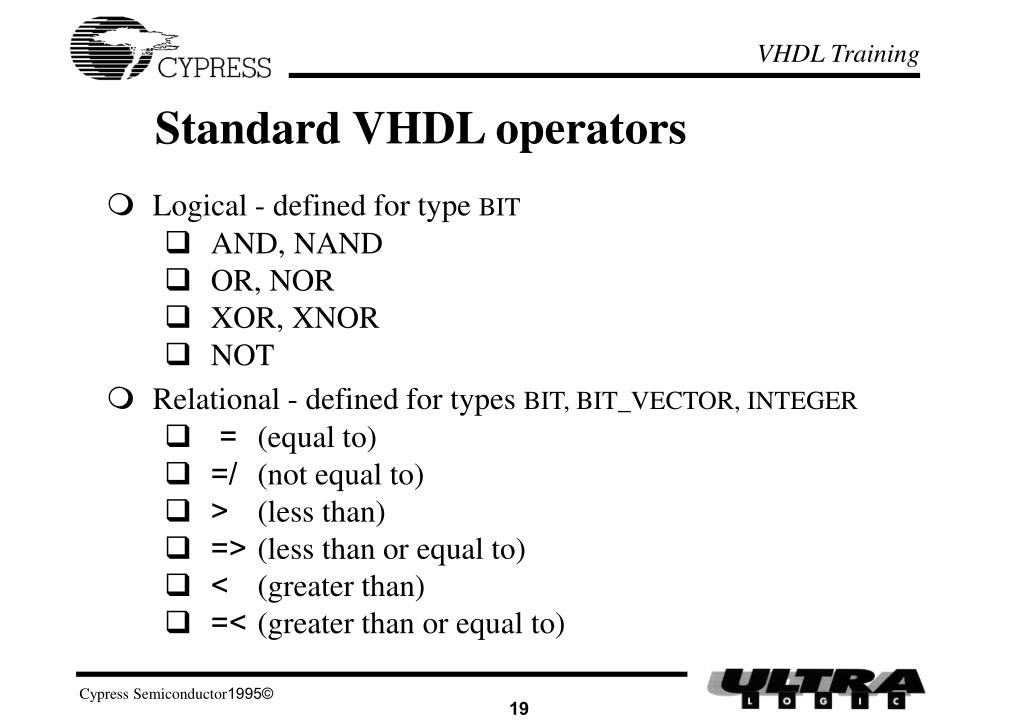

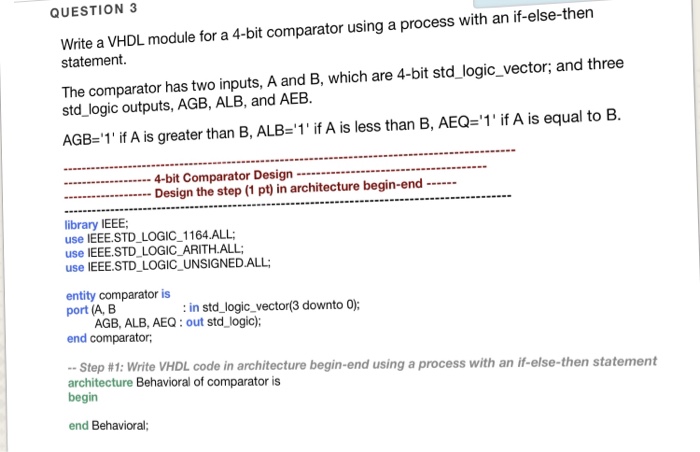

Relational Operators Result is boolean: greater than (>) less than (<) inequality (/=) greater than or equal to (>=) less than or equal to (<=) equal (=) - ppt download

Relational Operators Result is boolean: greater than (>) less than (<) inequality (/=) greater than or equal to (>=) less than or equal to (<=) equal (=) - ppt download

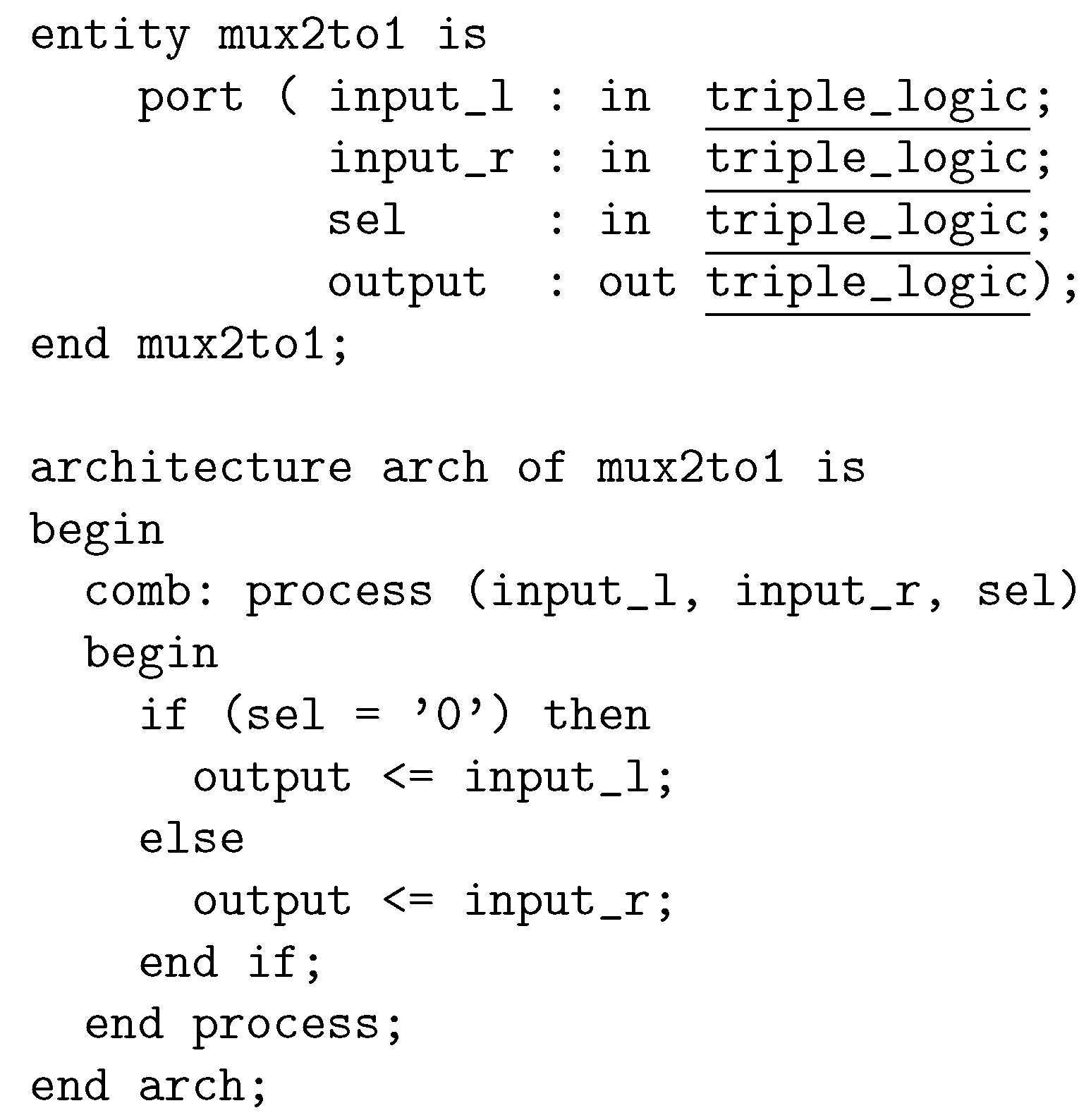

Electronics | Free Full-Text | Fine-Grain Circuit Hardening Through VHDL Datatype Substitution | HTML